加减运算电路实验

实验目的

-

理解使用加法器实现补码加减运算的原理。

-

掌握溢出判断方法。

-

学会使用Digital仿真软件的符号扩展器等几个有用的组件。

-

学会使用表达式生成电路图。

实验原理

加减运算

加法运算是最基本的算术运算,其运算速度对计算机的运行速度有着重要影响。 4位的加法器可以用4个全加器级联构成,由于存在进位链的传递延时,运算速度随着精度的提高(位数增加)而降低。所以实际的并行加法器并不会采用全加器级联的方法,而是采用先行进位加法器。

| Digital仿真软件无法精确仿真加法运算的电路延迟,所以实验不考虑并行加法器的实现细节,而是侧重于功能仿真,可以直接使用加法器组件。 |

由于补码加法可以连同符号位在内一起运算,并且补码减法可以转换为加法,所以在计算机中通常采用补码进行加减运算。其基本公式如下:

[X+Y] 补 =[X] 补 +[Y] 补

[X−Y] 补 =[X] 补 +[−Y] 补

这两个公式是补码加减运算的理论依据,它们所包含的意义是:

-

求两个数的和,可以先将这两个数的补码相加,所得到的结果就是这两个数和的补码;

-

求两个数的差,可以转换为加法进行计算。将第一个数的补码加上第二个数相反数的补码,所得到的结果就是这两个数差的补码。

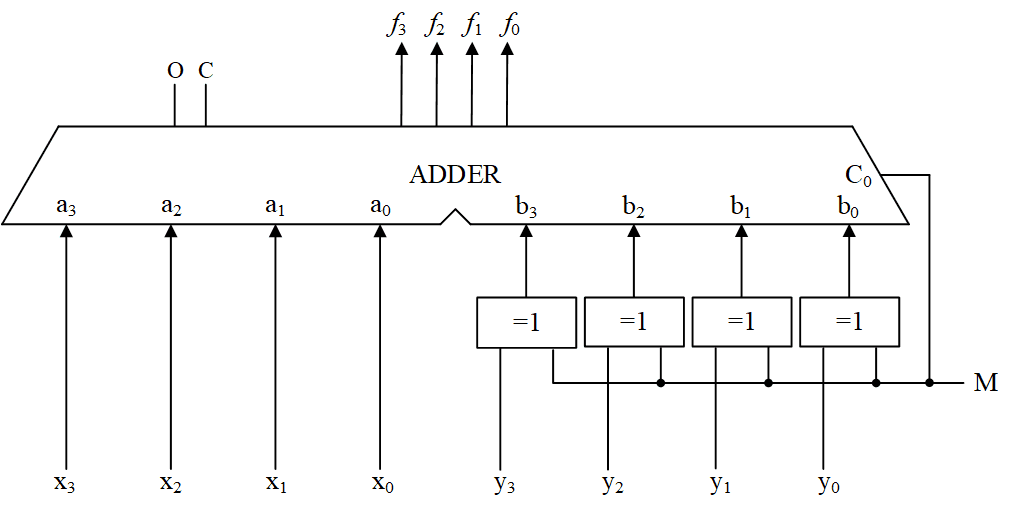

也就是说可以利用二进制加法器进行补码加减运算,只需要在加法器的基础上增加求补电路就可以实现减法,无需为减法设计专门的电路。 根据上述原理可以设计出补码加减运算电路如图 1所示。

图中ADDER是二进制加法器,实现的加法运算为F=A+B+C0;其中ai=xi,bi=yi⊕M,C0=M。

当M=0时,bi=yi⊕0=yi,C0=0,所以F=X+Y;

当M=1时,![]() ,

C0=1,故

,

C0=1,故![]() 。

。

可见,M用来控制是将Y送到加法器运算,还是将Y求相反数后再相加。 当M=0时做加法运算,M=1时做减法运算。

补码加法运算的溢出检测

溢出(overflow)是指运算结果超出了数的表示范围。 通过上面的讨论可知,有符号数的补码加减运算和无符号数的加法运算可以用同一个电路实现。 对于4位二进制编码,无符号数的表示范围是0~15,补码表示的带符号数的范围是−8~+7。 如果用图 1电路进行无符号数运算,结果大于15会产生进位,因此根据进位C值就可以判断无符号数的加法是否溢出。 但是补码加法运算是否溢出并不能根据进位来判断。下面介绍一种便于实验电路实现的补码加法运算的溢出检测方法——根据两个操作数的符号位和结果的符号位是否一致进行判断。

两个参加运算的数据如果符号相异,做加法时是不会产生溢出的。只有两个相同符号的数做加法运算时才有可能产生溢出。换句话说,两个正数相加结果为负数,或者两个负数相加结果为正数,均表示运算结果溢出。检测方法如下:

假设As和Bs表示两个操作数的符号,Fs表示运算结果的符号,则溢出检测的逻辑表达式为:

当两个加数为负数(As=Bs=1),而结果为正数(Fs=0)时,或者当两个加数为正数(As=Bs=0),而结果为负数(Fs=1)时,OV=1,即发生溢出。

| 需要说明的是,上面的讨论是针对加法运算。同理不难找出补码减法运算的溢出检测方法。但实际上,因为减法是转换为加法运算的,只要检测时使用B的符号而不是Y的符号,并不需要为减法运算另外设计溢出检测电路。 |

实验任务

1. 设计加减运算电路

下面给出几点说明。

-

加法器组件位于“Components/组件 ➤ Arithmetic/运算器 ➤ Adder/加法器”。

-

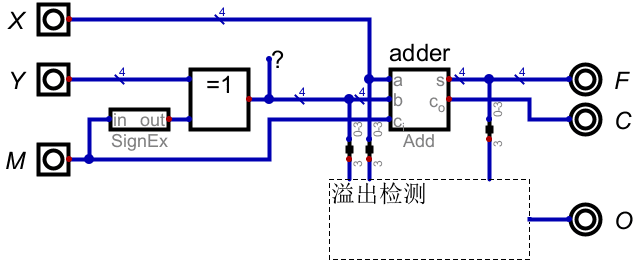

图 1原理图的X、Y都是4位的,所以异或运算用了4个1位的异或门;而图 2为了画图的简洁,使用1个4位的异或门。但控制信号M仍然是1位的,因此需要用“Sign extender/符号扩展器”组件扩展为4位。

-

为便于观察异或门输出的数据,添加了一个“Probe/探测器”组件(图中显示问号的那个)。

-

图 2未给出溢出检测电路。根据上面介绍的溢出检测方法,可以在Digital仿真软件中用如下表达式生成溢出检测电路。

let OF = As & Bs & ~Fs | ~As & ~Bs & Fs然后将生成的电路复制到加减电路中(复制时不要包含输入输出引脚),代替图中的溢出检测虚线框。 图 2为了从4位数据中抽取最高位作为符号位,使用了3个“Splitter/分裂器”组件;将这3个组件的输出端与溢出检测电路的相应输入端连接。

2. 验证加法运算

-

实验数据记录

设置M=0,按表 1步骤操作,填写加法运算的结果,并仿照第①行的形式写出运算数和结果的真值。

表 1. 加法运算数据记录表 行号

输入

输出

结果分析[注]

M

X

Y

F

O

C

视为无符号数

视为补码

标志位

①

0

1100

1011

0111

1

1

12+11=7(错)

(-4)+(-5)=7(错)

进位,溢出

②

0

1100

0101

③

0

0011

0101

④

0

1000

0001

⑤

0

1111

0001

⑥

0

⑦

0

注:真值按照电路的实际显示数据而非理论计算。

为方便分析运算结果,可以事先列出负数的4位补码与真值的对应关系:

补码

1000

1001

1010

1011

1100

1101

1110

1111

真值

−8

−7

−6

−5

−4

−3

−2

−1

-

实验数据分析。

分别针对无符号数和带符号数(补码),分析加法运算结果(包括标志位)。特别注意无符号数、带符号数加法溢出是由C标志反映还是由O标志反映,溢出时的运算结果是否正确。

3. 验证减法运算

-

实验数据记录

设置M=1,按表 2步骤操作,填写减法运算结果。

表 2. 减法运算数据记录表 行号

输入

输出

结果分析

M

X

Y

F

O

C

视为无符号数

视为补码

标志位

①

1

0101

0011

②

1

0011

0101

③

1

0111

1111

④

1

1000

1111

-

实验数据分析。

注意观察减法运算是否溢出和溢出标志的关系,是否产生借位和进位标志的关系。