时序电路仿真

时序电路由时钟驱动,在时钟边沿改变电路的状态。 下面以典型的时序电路组件D触发器为例,说明时序电路的仿真。

D触发器组件

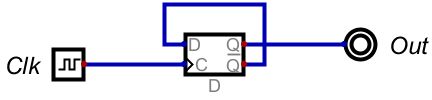

添加以下组件并连接。

-

添加“Components/组件 ➤ Flip-Flops/触发器 ➤ D-Flip-flop/D 触发器”。

-

添加“Components/组件 ➤ IO/输入输出 ➤ Input/输入”,将其命名为In,并连接到D触发器的D端口。

-

添加“Components/组件 ➤ IO/输入输出 ➤ Clock Input/时钟输入”,将其命名为Clk,并连接到D触发器的C端口。

-

添加“Components/组件 ➤ IO/输入输出 ➤ Outpu/输出”,将其命名为Out,并连接到D触发器的Q端口。

点击菜单项“Edit/编辑 ➤ Circuit specific settings/设置当前电路”,在对话框的“Advanced/高级设置”页面下勾选“Show measurement graph at simulation start/仿真启动时显示测量图”。

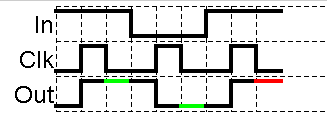

启动仿真,改变输入,观察输出变化。 可以看出,仅当Clk由0变1的瞬间,输出Out才会变化,其值与输入In相同。

仿真波形可以保存为图形文件。点击波形窗口的菜单项“File/文件 ➤ Export SVG / 导出SVG”,窗口中记录的波形将被保存为SVG图形文件。

| 新手入门中曾介绍了在启动仿真后点击菜单项“Simulation/仿真 ➤ Show measurement value table / 显示测量图”,这里介绍的在启动仿真之前设置电路属性的效果与其相同,不仅在需要多次启动仿真时省去了每次点击菜单的操作,而且在下面使用实时时钟的情况下能够及时记录仿真开始时的测量图形和数据。 |

实时时钟

右键点击Clk引脚,在属性窗口中勾选“Start real time clock/使用实时时钟”,“Frequency/频率”设置为1Hz(赫兹)。

断开D触发器的D输入端与输入引脚In的连接,将D触发器的反向输出端连接到D输入端,构成一个二分频器。如图 2所示。

启动仿真,可以看到Clk自动地翻转。如果设置频率为2或3赫兹,可看到Clk以更高的速度翻转。

从波形图可以看出,输出Out信号的周期是输入Clk信号的2倍,或者说输出信号的频率是输入信号的二分之一,即二分频。