硬布线控制实验(Ⅱ)

实验原理

指令部件

指令部件包括指令存储器和程序计数器。根据指令系统的设计,指令存储器的字长是14位。作为实验计算机,只需要存放简单的程序,所以指令存储器的容量只有16个存储单元,可以存放16条指令。因此指令存储器的地址需4位,由程序计数器PC提供。复位时PC值为0,即第一条指令的地址。在Clk上升沿到来时,如果Load为1,则将imm装入PC,实现程序转移;否则PC值加1,即顺序执行。

控制器

控制器以指令opcode作为输入,为数据通路中所有单元产生控制信号。

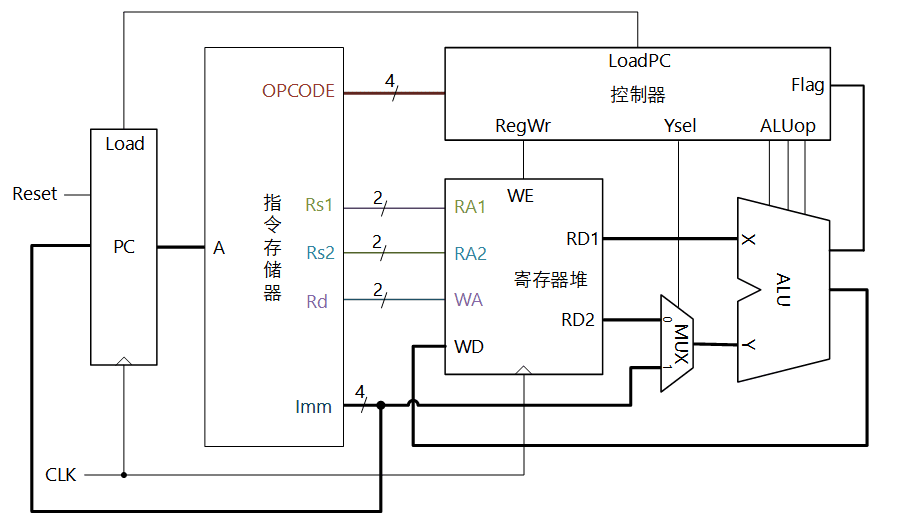

图 1单周期数据通路中,需要产生如下控制信号:

-

多路器的选择信号Ysel:为0时,选择将寄存器堆的RD2输出数据送给ALU的Y输入端;为1时,ALU的Y操作数来自指令中的立即数imm。

-

ALU的运算控制信号:根据前面ALU实验的设计,需要产生ALU的M、S0、S1控制信号。

-

寄存器堆的写允许信号RegWr:为1时,当在CLK时钟上升沿到来,寄存器堆执行写入操作。

-

PC装数使能信号LoadPC:为1时,PC装载来自指令中的立即数imm;为0时,PC加1。

因为指令系统的简单和规整,控制器的设计就是设计译码器来确定控制信号。对于指令系统中的R型和I型指令,控制器根据opcode的值,译码产生数据通路上的各个控制信号,实现指令功能。对于指令系统中的B型指令,控制器还需要来自ALU产生的标志位,与Opcode的值一起,译码产生控制信号。下面分别分析这两种类型的指令译码。

1.R型和I型指令的译码

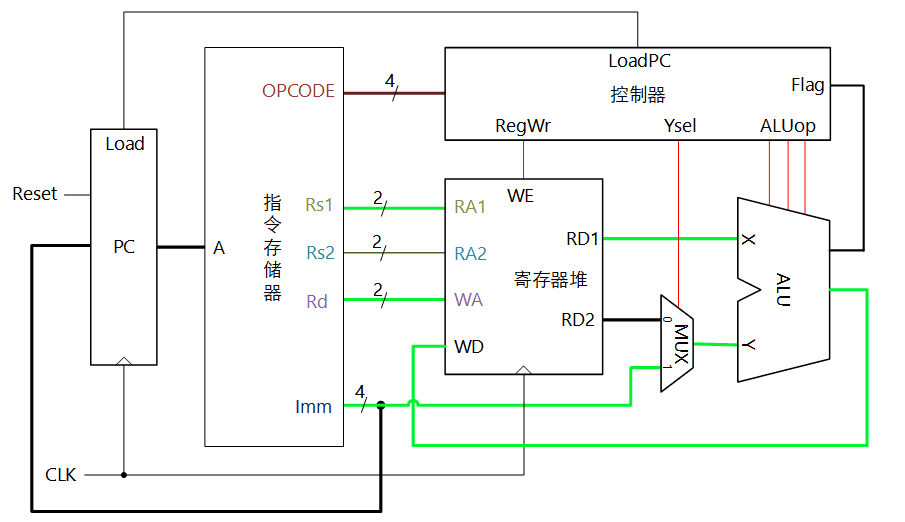

以“addi rd, rs1, #imm”指令为例,该指令将rs1寄存器的值与立即数imm相加,结果存入rd寄存器。 rs1寄存器的值已经通过寄存器堆的RD1连接到了ALU的X输入端。为了将立即数imm送给ALU的Y输入端,需要使多路器的控制信号Ysel为1。ALUop应控制ALU进行加法运算,如果采用前面实验的ALU电路,控制信号M、S0、S1均为0。为了将运算结果写入寄存器堆,RegWr信号应为1。而LoadPC信号应为0,因为addi不是分支指令,不会产生程序转移。 图 2数据通路图直观地反映了上述分析,绿色通路表示有效的信息流,红色表示有效的控制信号。

指令译码的真值表如表 1所示。表中只给出了addi指令的控制信号取值,类似地可以分析出其他指令的控制信号取值。有了真值表,就可以进一步得到指令译码器的电路。

| 指令助记符 | opcode | RegWr | Ysel | M | S0 | S1 | branch | brType0 | brType1 |

|---|---|---|---|---|---|---|---|---|---|

add |

0001 |

||||||||

sub |

0010 |

||||||||

and |

0011 |

||||||||

or |

0100 |

||||||||

xor |

0101 |

||||||||

addi |

0110 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

andi |

0111 |

||||||||

ori |

1000 |

||||||||

xori |

1001 |

||||||||

beq |

0110 |

||||||||

bne |

1011 |

||||||||

blt |

1100 |

||||||||

bge |

1101 |

注:表中2位brType是为下面分支指令预留,运算指令全部填0即可。

2.分支指令

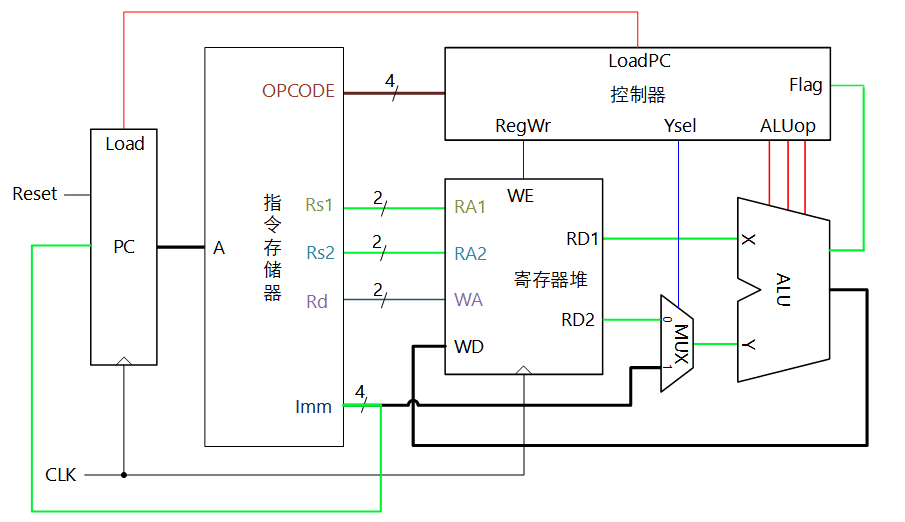

以“beq rs1, rs2, #imm”指令为例,该指令比较rs1和rs2寄存器的值是否相等,如果相等,则程序转移,下一条指令的地址由imm给出;如果不相等,则顺序执行。 转移发生时分支指令的信息流如图 3所示,绿色通路表示有效的信息流,红色和蓝色表示控制信号。

当转移发生时,控制信号LoadPC=1,将转移地址装入PC;如果不发生转移,LoadPC=0,PC加1。 可见,LoadPC并不是固定为1或为0,而是要根据比较运算的结果决定程序是否转移。所以,LoadPC不能单纯根据opcode产生。 opcode只能分辨是不是分支指令以及比较的类型,还需要与比较运算配合,才能产生控制信号。

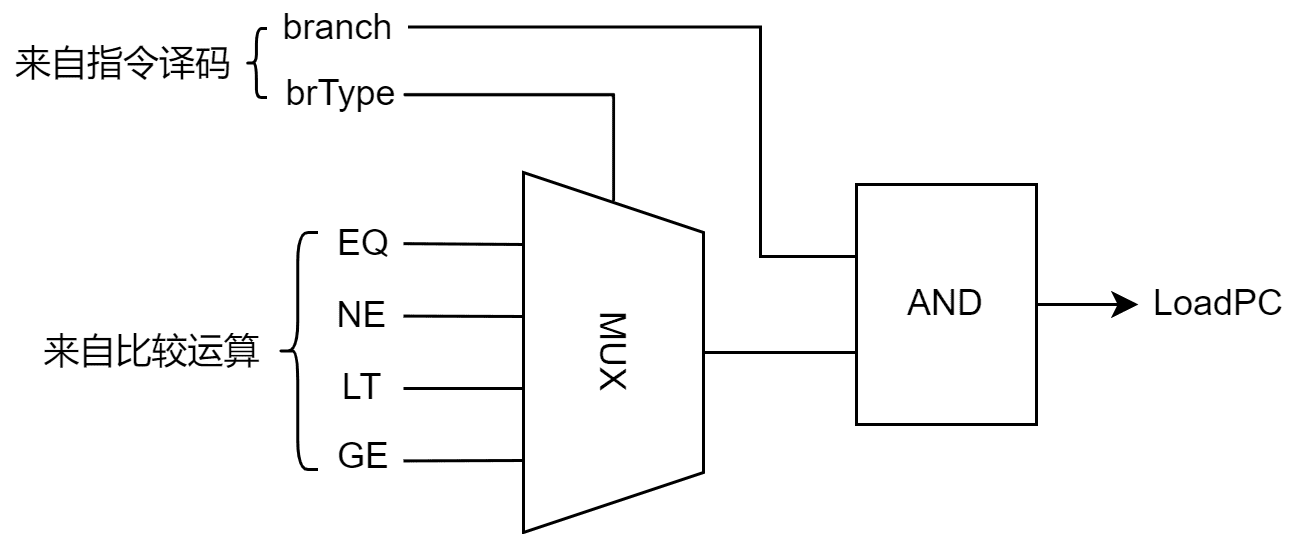

图 4给出了转移信号的生成方法。 其中EQ、NE、LT、GE是比较的结果,分别表示相等、不等、小于、大于等于,可以采用前面比较运算实验的结果。 4选1多路器用来从4种比较结果中选择一个。2位的选择信号brType由指令译码根据分支指令的类型产生。 多路器输出的信号还不能直接作为LoadPC信号,还要判断当前指令是不是转移指令。所以由branch信号控制与门,如果不是分支指令,LoadPC为0;是分支指令,再将多路器的输出作为LoadPC,也就是根据指令类型和比较结果决定程序是否转移。

表 2给出了beq指令的控制信号取值。

| 指令助记符 | opcode | RegWr | Ysel | M | S0 | S1 | branch | brType0 | brType1 |

|---|---|---|---|---|---|---|---|---|---|

beq |

0110 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

bne |

1011 |

||||||||

blt |

1100 |

||||||||

bge |

1101 |

实验任务

-

设计控制器

-

连接电路

按照图 1将各个子电路连接起来,并添加Reset输入引脚和CLK时钟输入引脚。

程序计数器PC可使用可预置数的计数器组件,该组件位于菜单项“Components/组件 ➤ Memory/存储器 ➤ Counter with preset / 计数器(可预设)”。

-

仿真验证

因为控制器的作用是控制指令的执行,所以需要通过执行指令来检验控制器的设计。例 1给出了一个测试程序的例子。

例 1. 分支指令测试程序示例0: 0x1815 addi r1, r0, #5 1: 0x202a ori r2, r0, #10 2: 0x09b0 sub r3, r1, r2 3: 0x2ec0 bne r2, r3, #0

上面测试程序使用的指令种类有限,自己编写程序进行更全面的验证。

-

运行斐波那契数列计算程序

-

将概述中斐波那契数列计算程序的机器码作为ROM的数据。

-

仿真运行程序,验证结果是否正确。

-

-

实验结果分析

对仿真结果进行分析。