单周期数据通路实验(Ⅰ)

实验原理

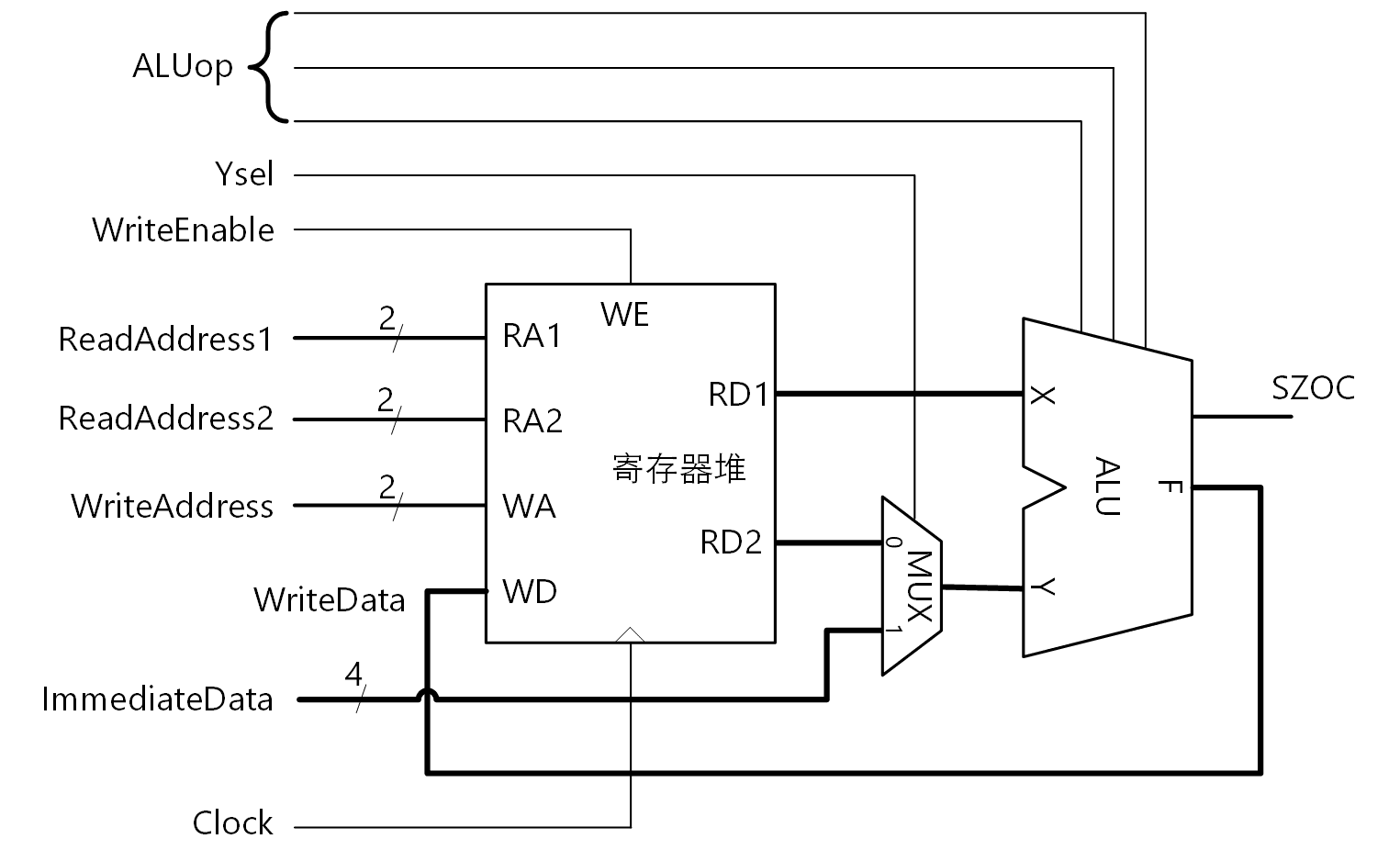

图 1是本实验的单周期数据通路,该数据通路使用了前面实验中的ALU和三端口寄存器堆。 ALU输入端X的运算数据来自寄存器堆的RD1读端口,另一个输入端Y的运算数据可以来自寄存器堆的RD2读端口,或者来自立即数。 寄存器堆写端口WD的数据来自ALU的运算结果F。 该数据通路可以在一个周期内完成从寄存器堆读数据、ALU运算、运算结果保存到寄存器堆。

图 1. 单周期数据通路

实验任务

-

设计

用Digital仿真软件按照图 1绘制电路图。 ALU和三端口寄存器堆使用前面实验完成的。

-

仿真

通过仿真验证数据通路,并保存仿真过程数据文件。

-

将2个常数存入R1、R2寄存器

常数通过ImmediateData输入引脚送入。从图 1可以看出,ImmediateData并没有直接连在寄存器堆的写端口,而是经过多路器后送到了ALU的Y输入端;所以要将ImmediateData送到寄存器堆的写端口,必须经过ALU。在前面寄存器堆的实验中已经设计R0寄存器的值恒为0,可以用ALU将ImmediateData加上R0寄存器值,将ImmediateData传送到寄存器堆的写端口。

存入的常数应有助于判别下面将要验证的各种运算结果是否正确。

可以手动操作完成验证,或者编写测试用例(test case)进行电路测试。 例 1给出了将“5”存入R1寄存器的测试数据。

例 1. 将“5”存入R1寄存器Clk WE WA RA1 RA2 IM Ysel M S0 S1 F S Z O C 0 1 0 0 0 0x5 1 0 0 0 0x5 0 0 0 0 (1) 1 1 0 0 0 0x5 1 0 0 0 0x5 0 1 0 0 (2)1 将“5”写入R1寄存器; 2 读出R1。 -

完成以下运算并验证结果是否正确。

R1 + R2 → R3;

R1 − R2 → R3;

R1 & R2 → R3;

R1 | R2 → R3;

R1 ⊕ R2 → R3;

R2 ⊕ 0b1111 → R3;

-

-

实验结果分析

对测试结果进行详细分析说明,并给出结论。

在结果与预期不符的情况下,尝试独立分析故障现象并排除故障,锻炼分析问题与解决问题的能力。