硬布线控制实验(Ⅲ)

实验原理

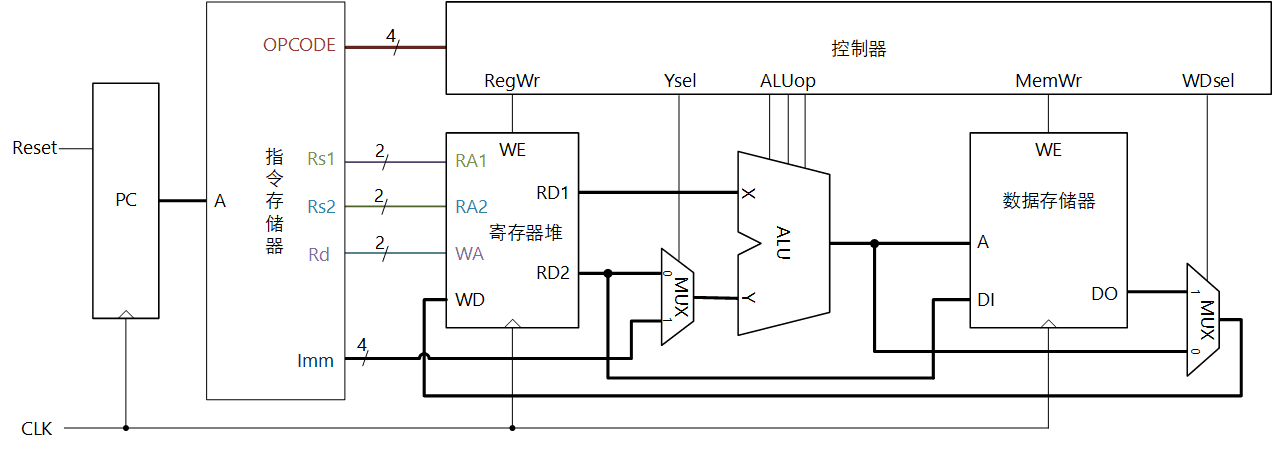

本项目是在硬布线控制实验Ⅰ或Ⅱ的基础上增加对存储器访问指令的支持。图 1给出在Ⅰ的基础上支持访存指令的原理框图,未支持分支指令。如果已经完成硬布线控制实验Ⅱ,读者不难画出在Ⅱ的基础上支持访存指令的原理框图。

图 1增加了如下控制信号:

-

数据存储器的写允许信号MemWr:为1时,当在CLK时钟上升沿到来,存储器执行写入操作。

-

多路器的选择信号WDsel:为0时,选择将ALU的运算结果送给寄存器堆的写数据端WD;为1时,将从存储器读出的数据送至WD。

下面分析存储器访问指令的执行。

根据指令功能表中关于load、store指令的功能描述,load指令将指定存储单元的内容装入指定寄存器,store将指定寄存器内容写入指定存储单元。 存储器的寻址采用变址寻址,变址寄存器号由rs1字段给出,偏移量由imm给出,所以有效地址EA=(rs1)+imm,即rs1指定的寄存器内容加上imm字段给出的偏移量作为有效地址。

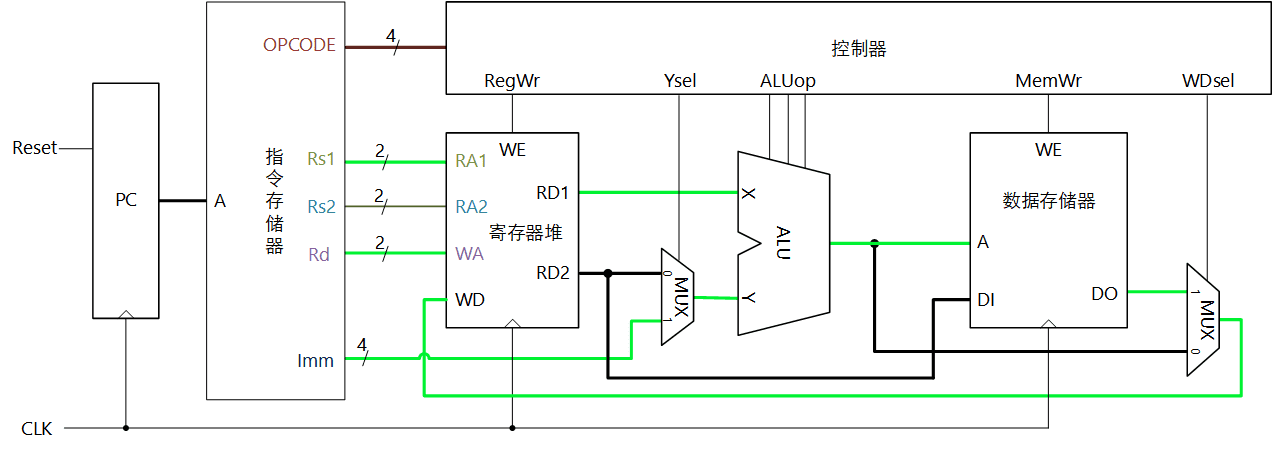

对于 load rd, rs1, #imm 指令,从存储器读出的数据写入寄存器,寄存器号由rd给出。load指令的信息流示意图如图 2所示,绿色通路表示有效的信息流。根据信息流通路,读者可分析出控制信号的取值。

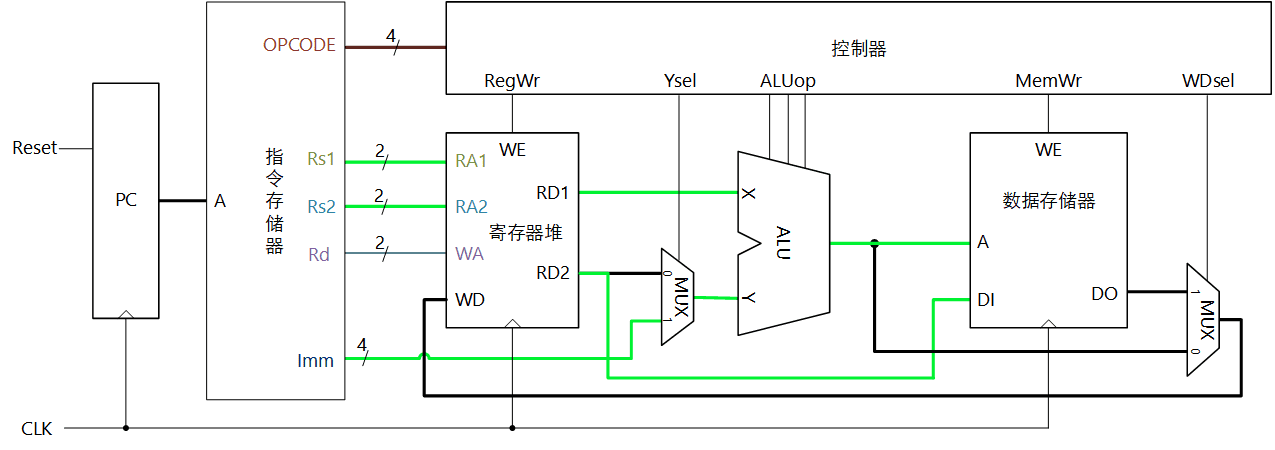

对于 store rs2, rs1, #imm 指令,源数据的寄存器号由rs2给出,该寄存器的内容将被写入存储器。store指令的信息流示意图如图 3所示,绿色通路表示有效的信息流。根据信息流通路,读者可分析出控制信号的取值。

实验任务

-

设计控制器

在硬布线控制实验Ⅰ或Ⅱ的基础上,扩充修改指令译码的真值表,使其支持访存指令。 然后使用真值表生成电路图。

-

连接电路

参考图 1原理图,如果已经完成硬布线控制实验Ⅱ,需在Ⅱ的基础上修改原理框图。按照原理图将各个子电路连接起来。

数据存储器使用存储器实验中已经熟悉的RAM组件。该组件位于菜单项“Components/组件 ➤ Memory/存储器 ➤ RAM ➤ RAM, separated Ports / RAM(独立端口)”。

-

仿真验证

例 1给出了一个测试程序的例子。

例 1. 访存指令测试程序示例0: 0x1815 addi r1, r0, #5 1: 0x202a ori r2, r0, #10 2: 0x09b0 sub r3, r1, r2 3: 0x3dc5 store r3, r1, #5 4: 0x3a10 load r1, r2, #0 5: 0x29c0 beq r1, r3, #0 (1)

1 硬件需支持分支指令。 -

实验结果分析

对仿真结果进行分析。