概述

计算机本质上是一个加工处理二进制信息的电路,包括ALU、寄存器、存储器等部件,这些部件通过信号线以某种方式连接起来,并且在控制器的控制下,使信息按照一定的规则在各个部件之间有序流动,完成信息的加工处理。这些信息加工部件及信息传递路径的总和就称为数据通路。

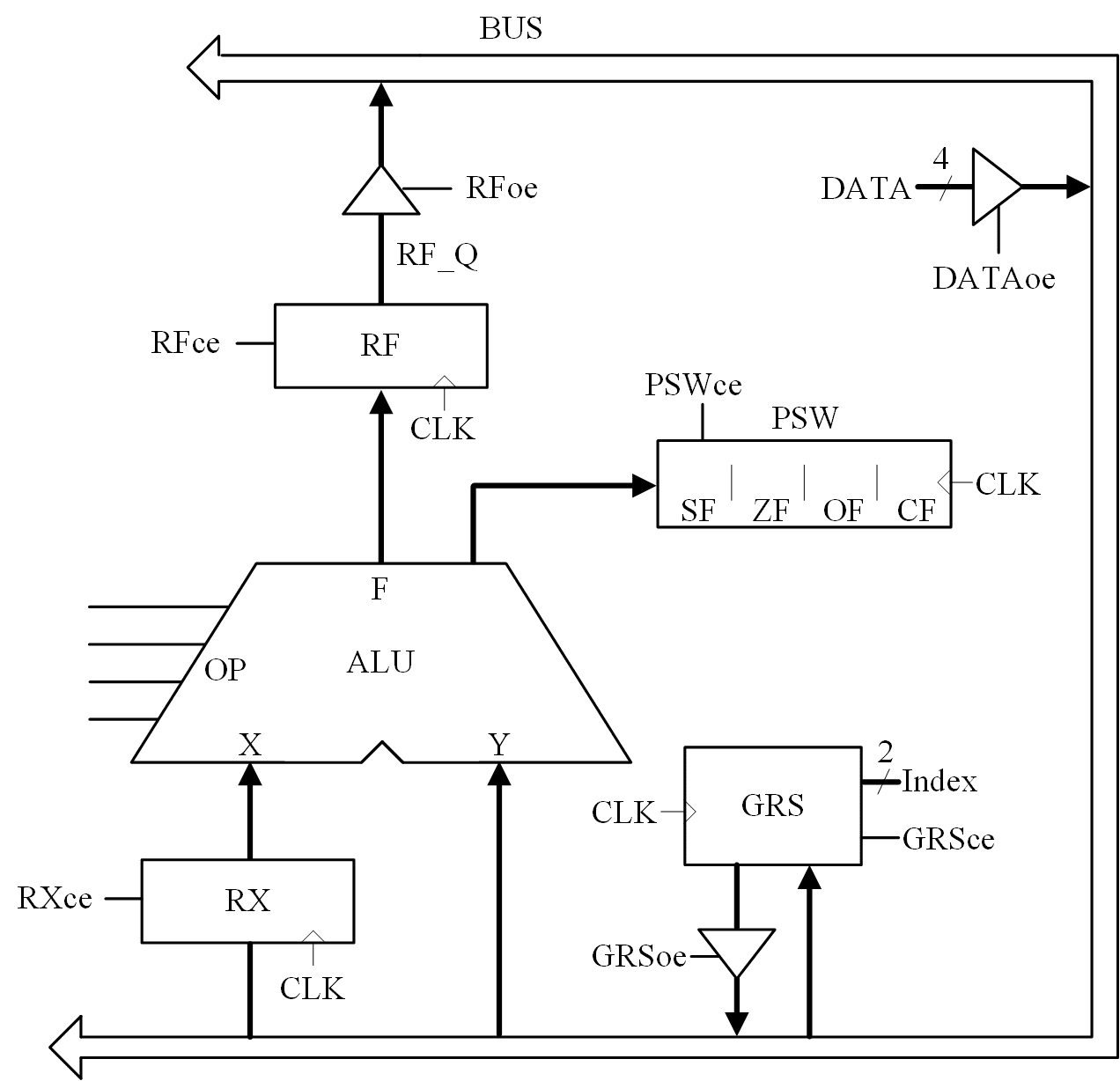

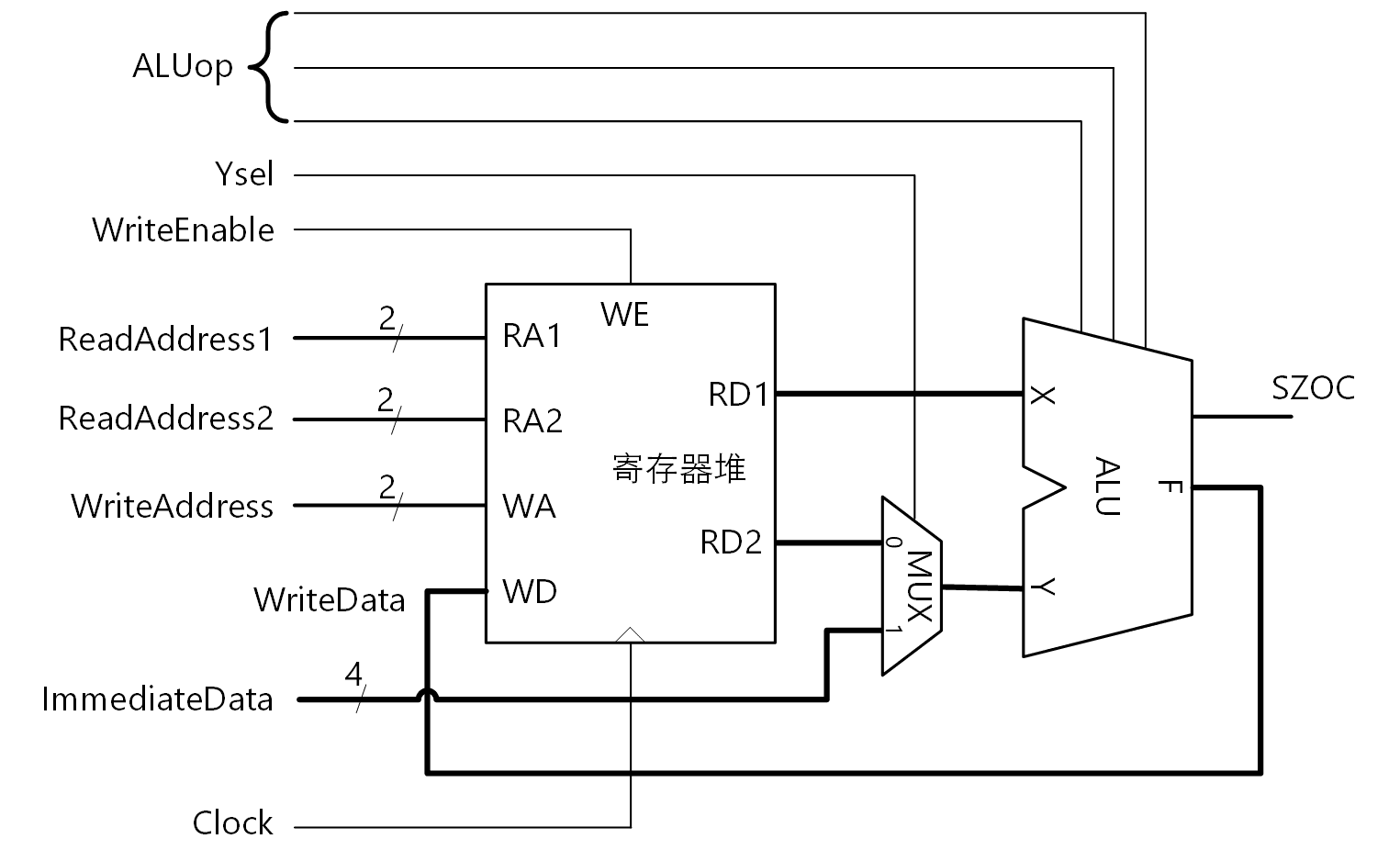

不同结构的数据通路在成本、速度及工作方式上有着较大差异。 图 1是一个单总线数据通路的例子,在这个数据通路上完成一次加法运算需要3个时钟周期。 图 2是另一种数据通路的结构,它只需要一个时钟周期就可以完成一次运算处理,称为单周期数据通路。 虽然不能单纯以时钟个数的多少来评价性能的优劣,但从发展历史来看,单总线数据通路是早期技术的产物,当时的主要考量是减少连接线的数量、降低成本。 而现代处理器更关注性能,普遍采用流水线数据通路。 而单周期数据通路更容易演变为流水线结构,所以这里只考虑单周期数据通路。

后面有两个单周期数据通路实验项目。第一个是图 2所示的数据通路,只包含了运算部件;第二个实验项目的数据通路增加了存储器。 可以根据需要完成其中一个,或者以递进的方式先后完成这两个项目。 在后面的控制器实验中,控制的对象就是这里完成的数据通路。

在数据通路实验之前,安排了寄存器堆实验,它是数据通路的必要组成部分。 寄存器堆内部包含若干个通用寄存器,用于暂存参加运算的数据和中间结果,这些寄存器的集合就称为通用寄存器组(Genral Register Set)。 寄存器组可以设计为单端口、双端口或三端口。单端口是指读出和写入共用同一组地址或数据端口,所以读出和写入不能同时进行,通常应用于多周期的数据通路,如图 1中的GRS。而双端口的读、写端口各自独立,在一个周期中可以同时读出和写入。三端口则有两个读端口和一个写端口可以同时操作,通常应用于单周期和流水线数据通路,如图 2所示。和早期的处理器相比,现代处理器的通用寄存器的数量更多,一般称为寄存器堆(Register File),也有译为寄存器文件。