寄存器堆实验

实验原理

CPU内部包含若干个通用寄存器,用于暂存参加运算的数据和中间结果,这些寄存器的集合就称为通用寄存器组(Genral Register Set)。 寄存器组可以设计为单端口、双端口或三端口。单端口是指读出和写入共用同一组地址或数据端口,所以读出和写入不能同时进行,通常应用于多周期的数据通路。而双端口的读、写端口各自独立,在一个周期中可以同时读出和写入。三端口则有两个读端口和一个写端口可以同时操作,通常应用于单周期和流水线数据通路。和早期的处理器相比,现代处理器的通用寄存器的数量更多,一般称为寄存器堆(Register File),也有译为寄存器文件。本实验完成三端口寄存器堆。

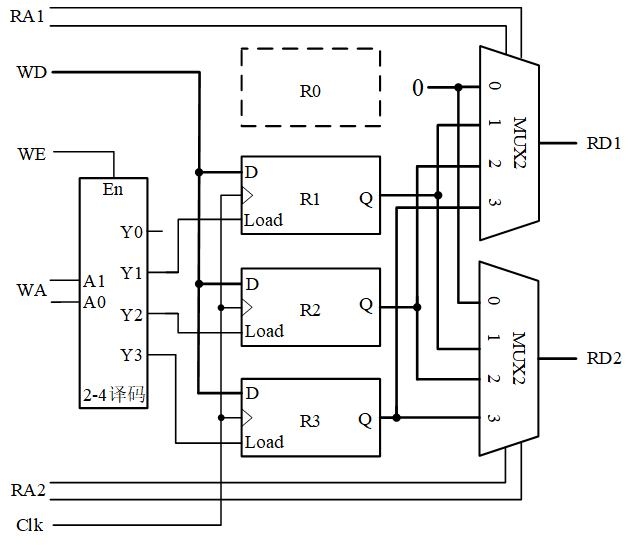

图 1是具有2个读端口和1个写端口的三端口寄存器堆的电路结构。其中RA表示读端口地址(Read Address),RD表示读端口数据(Read Data);WA表示写端口地址(Write Address),WD表示写端口数据(Write Data);WE是写使能(Write Enable)。

图 1. 三端口寄存器堆的框图